Hybrid Digital-Analog Circuits Can Increase Computational Power of Chaos-Based Systems

New research from North Carolina State University has found that combining digital and analog components in nonlinear, chaos-based integrated circuits can improve their computational power by enabling processing of a larger number of inputs. This “best of both worlds” approach could lead to circuits that can perform more computations without increasing their physical size.

Computer scientists and designers are struggling to keep up with Moore’s law, which states that the number of transistors on an integrated circuit will double every two years in order to meet processing demands. They are rapidly reaching the limits of physics in terms of transistor size – it isn’t possible to continue shrinking the transistors to fit more on a chip.

Chaos-based, nonlinear circuits have been proposed as a solution to the problem, as one circuit can perform multiple computations instead of the current “one circuit, one task” design. However, the number of inputs that can be processed in chaos-based computing is limited by ambient noise, which decreases accuracy. Ambient noise refers to random signal fluctuations that can be caused by temperature variations, voltage fluctuations or semiconductor defects.

“Noise has always been a big problem in almost all engineering applications including computing devices and communications,” says Vivek Kohar, postdoctoral research scholar at NC State and lead author of a paper describing the work. “Our system is nonlinear and so noise can be even more problematic.”

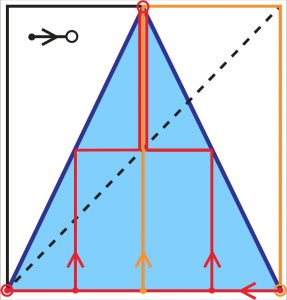

To address the problem, the researchers created a hybrid system which uses a digital block of AND gates and an analog nonlinear circuit to distribute the computation between the digital and analog circuits. The result is an exponential reduction in computational time, which means that the output can be measured while the noise-based deviations are still small. In short, the computations are performed so quickly that noise doesn’t have time to affect their accuracy.

To further improve the accuracy, Kohar and his colleagues’ proposed solution couples multiple systems. This coupling provides a safety net that reduces the effect of noise-based deviations at the final stage.

“Think about mountaineering,” says Kohar. “The climbers can climb individually but if one slips then he/she may have a dangerous fall. So they use ropes to connect them with each other. If one slips, the others will prevent their fall. Our system is somewhat like this, where all the systems are connected with each other all the time.

“The systems are tuned in such a way that at the time of measurement, our system is at the maxima or minima – the points where the effects of noise are low in general and much lower if the systems are coupled. Considering the mountaineering example again, this means that we take the averages of climbers when they are at resting locations like the peak or in a valley, where the distances between them are smallest.”

The research appears in Physical Review Applied. Kohar is first author. Behnam Kia, research assistant professor of physics at NC State; William Ditto, dean of the College of Sciences at NC State; and John Lindner, professor of physics at The College of Wooster, contributed to the work. The research was funded by the Office of Naval Research under grant N00014-16-1-3056 and STTR grant N00014-14-C-0033.

-peake-

Note to editors: An abstract of the work follows.

“Implementing Boolean Functions in Hybrid Digital-Analog Systems”

DOI: 10.1103/PhysRevApplied.7.044006

Authors: Vivek Kohar, Behnam Kia, William Ditto, North Carolina State University; John Lindner, The College of Wooster

Published: Physical Review Applied

Abstract:

We propose an architecture to implement multi-input one-output Boolean functions using chaos computing in hybrid digital-analog systems consisting of a digital block of conventional AND gates and a nonlinear circuit. This architecture efficiently utilizes the super-stable initial conditions of a nonlinear circuit and enables us to implement all possible 22m Boolean functions of m data inputs in just m iterations of the nonlinear circuit, resulting in better operating speed and noise tolerance. In an ideal nonlinear map, this architecture eliminates the need for a decoder, as the outputs are mapped to maxima and minima of the map and can be fed directly to the next stage, enabling multilayer concatenation. We demonstrate the utility of this architecture in a three-transistor circuit.

This post was originally published in NC State News.